ADALM2000实验:生成负基准电压

发布时间: 2023-08-17 14:33:46 来源:行业动态

本次实验旨在研究产生负基准电压的方法。正基准电压源或稳压器配置更常见。从正电压产生负基准电压的传统方法涉及反相

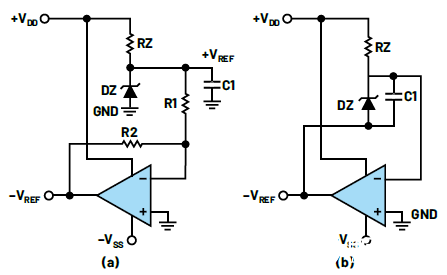

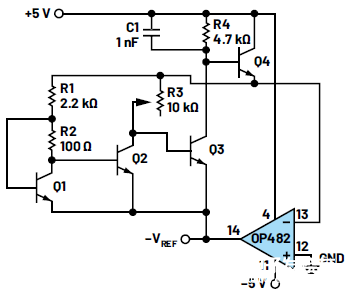

在图1a中,使用简单的电路产生正基准电压+VREF,该电路由来自齐纳二极管稳压器实验活动的RZ和DZ组成。正基准电压源通常包括一个同相运算放大器缓冲器,用于调整输出电压并提供负载所需的任何电流。产生负基准电压的显而易见的方法是使用反相运算放大器级。运算放大器将+VREF反相,在输出端提供-VREF。这种方法需要两个精密电阻R1和R2。这两个电阻的匹配误差(例如,不同的精度和不同的温度系数)以及运算放大器中的电压失调,会在运算放大器的输出端(+VREF)产生误差,如图1a所示。然而,这种反相放大器配置的一个潜在附带好处是-VREF不需要具有与+VREF相同的绝对值。通过改变R1和R2的比值,可以放大或缩小负基准电压。我们将在本实验活动中研究的另一种配置如图1b所示。它能产生负基准电压,不依赖于成比例的匹配电阻,并有可能以更少的元件提供更高的精度。

图1.生成-VREF的两种可能方法:(a)使用两个匹配电阻(R1和R2)的标准方法,以及(b)不使用电阻的更高精度方法

考察图1a不难发现,由于反相运算放大器配置的虚地特性,齐纳电压+VREF作用于电阻R1上。如果R2正好等于R1,则同一电压VREF也会出现在R2上,但相对于地的符号相反。R2两端的电压与齐纳二极管两端的电压相同,因此我们实际上可以用反馈环路中的二极管代替R2,如图1b所示,并且仍然在-VREF处产生相同的电压。RZ只是设置齐纳二极管中的偏置电流水平,与图1a中的RZ非常相似。在图1b中,IZ等于VDD/RZ,而在图1a中,IZ等于(VDD – +VREF)/RZ。为使两种情况下的设计具有相同的IZ,我们仅需更改RZ的值。电容C1解耦接地端和输出端之间的基准二极管。此外,具有低电感的0.1μF电源解耦电容(图1中未显示)通常连接到+VDD和-VSS,非常靠近运算放大器。

理论上,此电路能利用几乎任何三端基准电压源电路和低噪声、低失调运算放大器来构建。为了基于带隙概念构建负基准电压源,我们原本需要高质量PNP晶体管,但当前IC工艺中普遍使用的PNP,其质量不如现有NPN器件高。这些基于NPN的带隙电路将提供若干例子,我们可通过这些例子来探索该负基准电压源的配置。本实验第1步中的第一次电路迭代将使用二极管作为基准,后续迭代将代之以基于NPN晶体管的双端(并联)和三端(串联)电路作为基准元件。

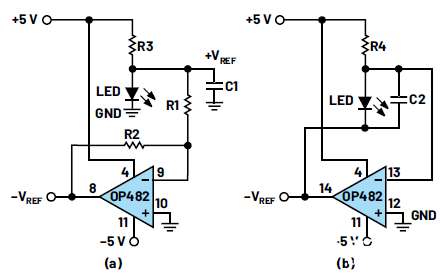

部件套件中提供的齐纳二极管(1N4735)是6.1 V二极管。6.1 V的反向击穿电压太高,无法使用ADALM2000

的固定±5 V电源来构建该电路。LED的正向电压在1.6 V至2.0 V范围内,具体取决于二极管的颜色。虽然它不是合适的基准二极管,但我们大家可以使用ADALP2000模拟部件套件中的LED构建教学用电路。

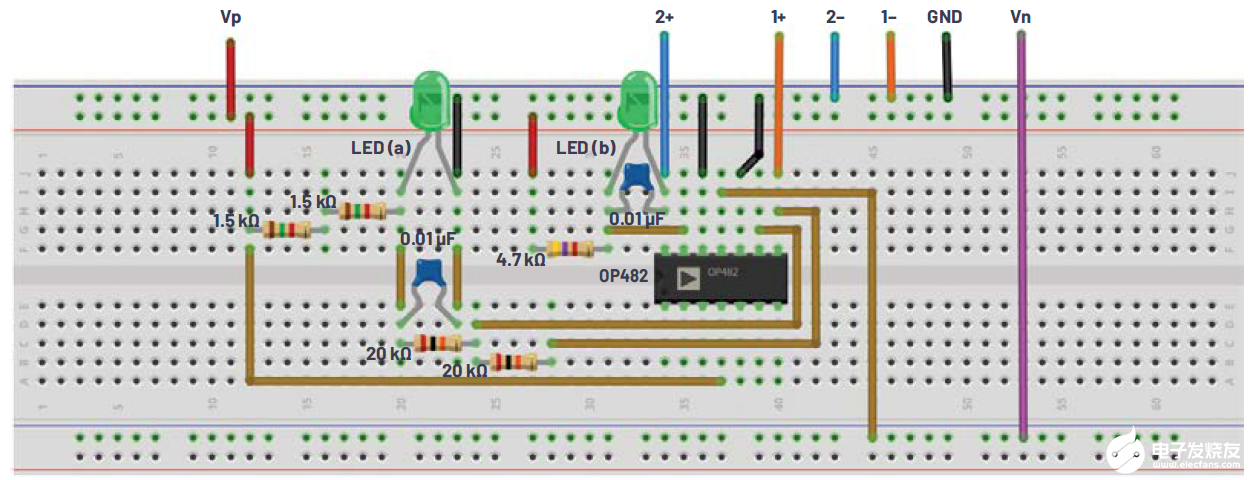

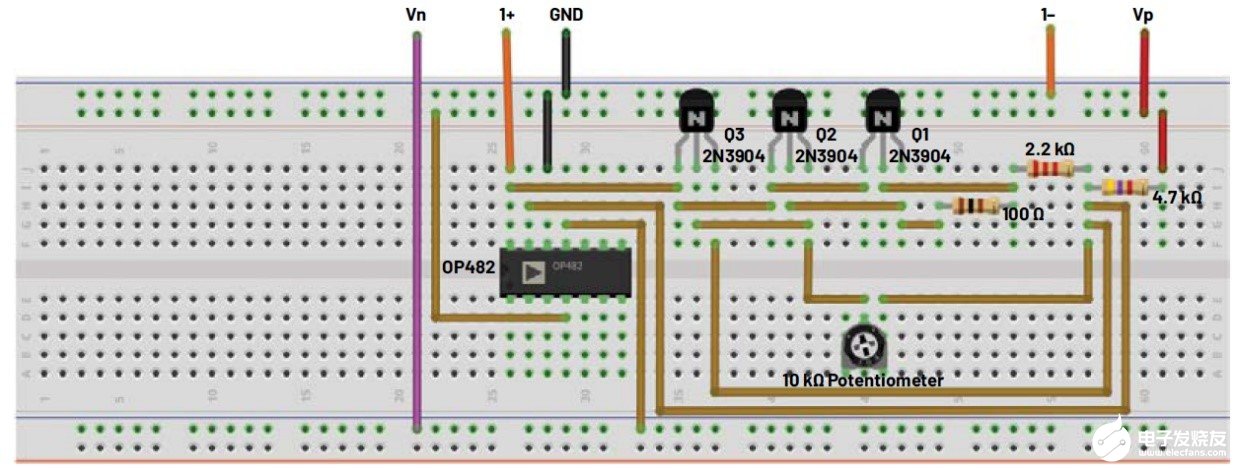

在无焊试验板上构建图2所示的图1a和图1b两个版本的电路。最好使用两个颜色相同的LED。绿光LED的正向压降高于红光或黄光LED。我们希望二极管电流ID约为1 mA。在两个版本的电路中,电流ID应接近相同的值(见图1a和图1b)。在情况a中,ID将为(+5 V – VD)/R3。在情况b中,ID将为+5 V/R4,因此4.7 kΩ电阻将产生约1 mA电流。如果使用2 V作为VD的估计值,则R3约为3 kΩ。将部件套件中的两个1.5 kΩ电阻串联,便可获得3 kΩ电阻。另外,对于情况a,我们需要选取R1和R2的值。我们希望R1中的电流比R3中的电流小得多。因此,R1和R2应设置为非常高的值,例如20 kΩ应满足该条件。

从Scopy软件中打开电压源控制和电压表窗口。能够正常的使用数字万用表(即DMM,如果有的话)来测量电路中的直流电压,其精度高于Scopy电压表。试验板连接如图3所示。

打开正负电源。观察-VREF处(运算放大器的引脚8和14)和LED上+VREF处的两个电压。

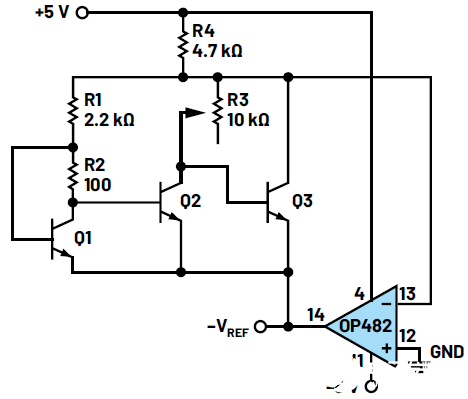

修改第1步中的试验板设置,如图5所示。对试验板进行任何修改之前,确保关闭电源。用并联稳压器替换LED。电阻R1和R2以及晶体管Q1连接为零增益放大器。如同在稳定

中一样添加电阻R3和晶体管Q2。若使用SSM2212匹配的NPN对,应将其用于器件Q1和Q2。添加Q3作为共发射极,其基极连接到Q2的集电极,集电极连接到R1、R3和R4的组合节点。

打开正负电源。观察-VREF处(运算放大器的引脚14)的电压和带隙并联稳压器(Q3的集电极和发射极)上的电压。可以调整电位计R3以产生-1.25 V基准电压。

为了测试+VDD的裕量要求,断开固定正电源与+VDD的连接,并移除所有电源解耦电容。对试验板进行任何更改或增加之前,确保关闭电源。现在将+VDD连接到AWG 1。将AWG 1设置为100 Hz的梯形波形。将幅度设置为5 V峰峰值,偏移设置为2.5 V,以获得0 V至+5 V摆幅。将

通道1连接到AWG1的输出端,并将示波器通道2连接到第一个示例电路的-VREF,即OP482的引脚14。在XY模式下使用示波器仪表,示波器通道为X,示波器通道2为Y。启动AWG 1,打开固定的-5 V电源。记录-VREF开始保持-1.25 V不变情况下的最小+VDD电压。

为了测试-VSS的裕量要求,将+VDD重新连接到固定正电源。断开固定负电源与-VSS的连接,并移除所有电源解耦电容。现在将-VSS连接到AWG 1。将幅度设置为5 V峰峰值,偏移设置为-2.5 V,以获得0至-5 V摆幅。启动AWG 1,打开固定的+5 V电源。重复测量OP482的引脚14,记录基准电压保持恒定情况下的最低-VSS值。

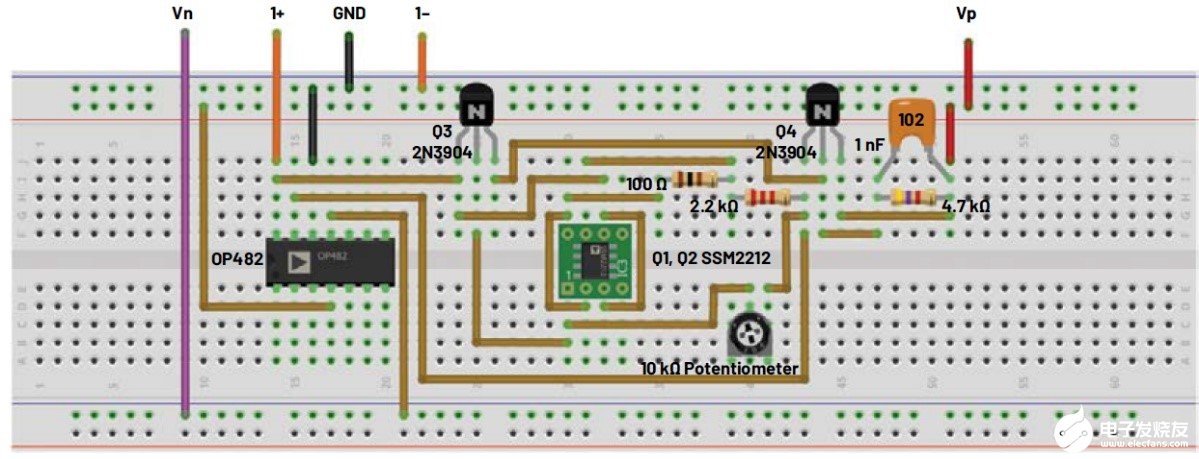

修改第1步中的试验板设置,如图7所示。对试验板进行任何修改之前,确保关闭电源。添加发射极跟随器Q4和补偿电容C1,将第2步中使用的双端并联稳压器变更为三端基准电压源。

打开正负电源。观察-VREF处(运算放大器的引脚14)的电压和带隙三端稳压器(Q4的发射极和Q3的发射极)上的电压。

1.对于图2中的电路,如果将绿光LED替换为红光或黄光LED,输出基准电压值会发生什么变化?

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。侵权投诉

都是利用的反相运放,然后要求精度的话需要两个精密匹配的电阻,然后我在网上看到的这个不用精密电阻的

内置采样速率可达 100MSPS 的12位模-数和数-模转换器,是一个高性能掌上

“稳定电流源”所示。附加材料两个小信号NMOS晶体管(M3和M4采用CD4007或ZVN2110A)图5.带尾电流源的差分对硬件设置第一个波形发生器配置为

概述 /

旨在研究一个使用NPN晶体管的简单差分放大器。首先,我们应该做一些关于硬件限制问题的说明。

:BJT差分对 /

(ADI公司)相连的电路及连接如图1所示。NPN晶体管Q1和Q2以及PNP晶体管Q3和Q4应从VBE匹配最佳的可用器件中选择。

:跨阻放大器输入级 /

:放大器输出级 /

室仪器。本文将使用Python编程语言,因为它的简单性,也因为它是开源的。通过Python和

创建示波器 /

室仪器。本文将使用Python这种简单的开源编程语言。将Python与

创建示波器 /

:使用CD4007阵列构建CMOS逻辑功能”中探讨的CMOS逻辑基础原理,并获取更多使用复杂CMOS门级电路的经验。具体而言,您将了解怎么样去使用CMOS传输门和CMOS反相器来构建D型触发器或锁存器。

:CMOS逻辑电路、D型锁存器 /

:可调外部触发电路 /

创建虚拟示波器 /

主动学习模块是一种经济实惠的USB供电软件定义仪器,内置以100 MSPS速率运行的12位ADC和DAC,可将高性能

高级主动学习模块ADI 官网现货发售! /

7天入门网络编程 - 4.使用 Socket 实现 UDP 服务器 #网络编程

会自己蹦离地面的毛绒玩具,拆开看看内部的工作机制是什么原理 #硬核拆解